Internship Positions at ICCL, UNIST

The Embedded Computing Laboratory at UNIST is recruiting

multiple undergraduate researchers in the broad area of

brain-inspired computing as described below.

FPGA-based Deep Learning

Recent advances in deep learning are in large part due to the increased computing capability of off-the-shelf processors. To enable further advances in this direction, this project explores the use of “programmable hardware”, or FPGA (Field-Programmable Gate Array) technology, for the acceleration of deep neural networks such as convolutional neural networks. In a broader context, this research topic is about the application of hardware-software co-design principles to machine learning algorithms, which has many implications and is in active research nowadays.

This topic is best suited for students majoring in both CSE and EE (it doesn’t matter whichever is the 1st major). Prerequisites include Computer Organization, and exposure to hardware description languages is a strong plus. Knowledge of Machine Learning or Artificial Intelligence is a plus, but not required.

Stochastic Deep Neural Network

Creating a Deep Neural Network (DNN) processor has many appeals. A DNN processor can be much more efficient than CPU/GPU/FPGA-based implementations, thus enabling a host of interesting applications (e.g., real-time image recognition), and being a processor, it can be applied to many different neural network applications. Challenges however include how to make it scalable to large and small networks. One idea is to apply Stochastic Computing (SC). SC is a new way of representing numbers and performing arithmetic operations, and radically different from conventional digital computing and enables much more compact implementations of complex functions.

Best candidates for this topic should have strong math skills (especially in probability). Machine learning or hardware design is not a requirement.

Interested students should contact Prof. Lee.

Note: These research positions are related to Samsung Future Technology Project.

Sponsored by Samsung Future Technology Center,

we have launched a new, ambitious project on brain-inspired computing,

titled Reconfigurable Deep Neural Network Processor Based on Stochastic Computing.

Old boys visiting ICCL lab today.

IEEE Spectrum introduces how neural circuitry implanted in our brain can do life-saving work. Though the article doesn’t give out much info about the kind of neural circuity implanted, it does mention microprocessor and battery. So it looks like a really low power microprocessor running some kind of algorithm similar to neural net. The article suggests that learning takes place offline, but is silent on how the parameter update can be done or how easy/unintrusive it is.

Either way it shows another very compelling application for embedded systems capable of machine learning tasks.

Bionic woman, but the striking similarity with Matrix is undeniable. (via IEEE)

Congratulations! Our paper “Optimizing Stream Program Performance on CGRA-based Systems,” authored by Hongsik Lee, Dong M. Nguyen, and Jongeun Lee (all currently at UNIST) is accepted to DAC (Design Automation Conference) this year. This work was in large part based on the work of Seongseok Seo, who graduated UNIST with a master’s degree one year ago. Seongseok’s primary work, which was presented at the last year’s CODES+ISSS conference, was about a light-weight yet highly effective hardware extension for mapping nested loops often found in DSP (Digital Signal Processing) applications. This work takes it to another level, developing application-level mapping strategies for stream applications with comparisons to GPU mapping results.

The DAC conference is frequently the highest ranked conference in the area of electronic design automation. It is also widely recognized as one of the most prestigious conferences in the electrical engineering and computer science discipline.

(Image from inhabitat.com via google image)

The 22nd Korean Conference on Semiconductors (KCS) is one of the largest conferences held in Korea in the electronic engineering discipline. Last year KCS attracted about 1,300 attendees from academia and industry. KCS also boasts a strong technical program consisting of about 300~400 oral+poster presentations annually.

This year the ICCL lab has three oral paper presentations, on high-level synthesis presented by Atul Rahman, coarse-grained reconfigurable architecture by Hongsik Lee, and application mapping for GP-GPUs (General-Purpose Graphics Processing Units) by Dong M. Nguyen.

Welcoming Atul!

Photo credit: Hyeon Uk took this photo.

Congratulations!

Our paper, titled “Flattening-based Mapping of Imperfect Loop Nests for CGRAs” by Jongeun Lee, Seongseok Seo, Hongsik Lee, and Hyeon Uk Sim, is accepted to this year’s CODES+ISSS (International Conference on Hardware-Software Codesign and System Synthesis).

CODES+ISSS is is a premier conference for embedded systems and hardware software co-design research, and held as part of ESWEEK (Embedded Systems Week) event, which also includes CASES (International Conference on Compilers, Architecture, and Synthesis for Embedded Systems) and EMSOFT (International Conference on Embedded Software), along with a host of workshops and symposia. Congratulations again to those who did the hard work!

Congratulations!

Our paper titled “Improving Performance of Loops on DIAM-based VLIW Architectures” in collaboration with SNU, was accepted for this year’s LCTES (Languages, Compilers, and Tools for Embedded Systems), a premiere conference on compilation for embedded systems. The conference will be held in Edinburgh, UK, in June.

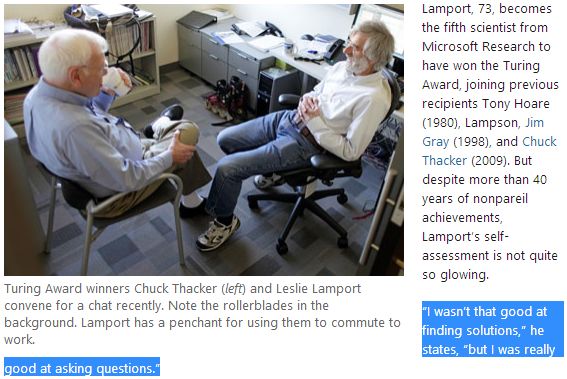

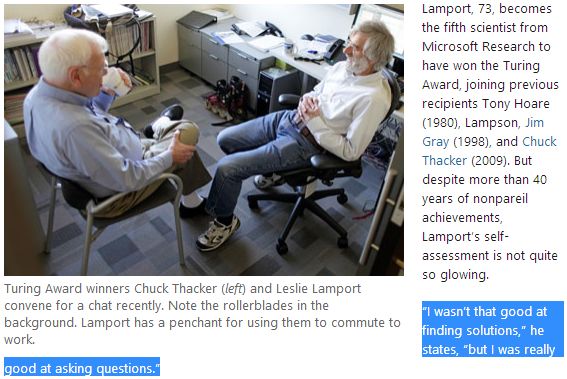

First I admit I myself am not a good questioner, especially in large lectures.

But I do realize the importance of asking questions as a means of learning and doing research, and encourage my students to do so (how?).

Here is a good article that may motivate you in that direction (see the bottom of the exerpt). This is on Leslie Lamport, this year’s Turing Award winner.

(excerpt is from http://research.microsoft.com/en-us/news/features/lamport-031814.aspx)