Architecture Optimization for AI Accelerators

Specializing CGRAs for Light-Weight Convolutional Neural Networks, Jungi Lee and Jongeun Lee**, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), November, 2021. (online publication)

NP-CGRA: Extending CGRAs for Efficient Processing of Light-weight Deep Neural Networks, Jungi Lee and Jongeun Lee**, Proc. of Design, Automation and Test in Europe (DATE), pp. 1408-1413, February, 2021.

Architecture-Accuracy Co-optimization of ReRAM-based Low-cost Neural Network Processor, Segi Lee, Sugil Lee, Jongeun Lee**, Jong-Moon Choi, Do-Wan Kwon, Seung-Kwang Hong and Kee-Won Kwon, Proc. of the 30th ACM Great Lakes Symposium on VLSI (GLSVLSI), pp. 427-432, September, 2020.

SparTANN: Sparse Training Accelerator for Neural Networks with Threshold-based Sparsification, Hyeonuk Sim, Jooyeon Choi and Jongeun Lee**, Proc. of ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), pp. 211–216, August, 2020.

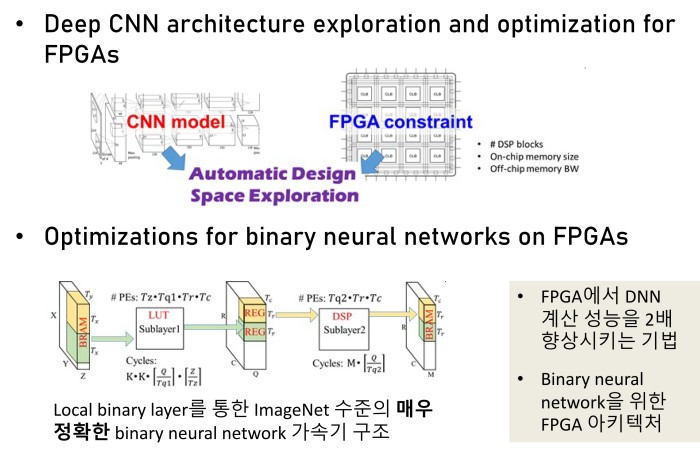

Double MAC on a DSP: Boosting the Performance of Convolutional Neural Networks on FPGAs, Sugil Lee, Daewoo Kim, Dong Nguyen and Jongeun Lee**, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 38(5), pp. 888-897, May, 2019.

Efficient FPGA Implementation of Local Binary Convolutional Neural Network, Aidyn Zhakatayev and Jongeun Lee**, Proc. of the 24th Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 699-704, January, 2019.

XOMA: Exclusive On-Chip Memory Architecture for Energy-Efficient Deep Learning Acceleration, Hyeonuk Sim, Jason H. Anderson and Jongeun Lee**, Proc. of the 24th Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 651-656, January, 2019.

FPGA Prototyping of Local Binary Convolutional Neural Network, Segi Lee, Aidyn Zhakatayev and Jongeun Lee**, Proc. of the 26th Korean Conference on Semiconductors, February, 2019.

Design Space Exploration of FPGA Accelerators for Convolutional Neural Networks, Atul Rahman, Sangyun Oh, Jongeun Lee** and Kiyoung Choi, Proc. of Design, Automation and Test in Europe (DATE), pp. 1147-1152, March, 2017.

Double MAC: Doubling the Performance of Convolutional Neural Networks on Modern FPGAs, Dong Nguyen, Daewoo Kim and Jongeun Lee**, Proc. of Design, Automation and Test in Europe (DATE), pp. 890-893, March, 2017.

Efficient FPGA Acceleration of Convolutional Neural Networks Using Logical-3D Compute Array, Atul Rahman, Jongeun Lee** and Kiyoung Choi, Proc. of Design, Automation and Test in Europe (DATE), pp. 1393-1398, March, 2016.